Who am I?

I'm a Ph.D. student in the Department of Information Engineering, University of Pisa. I received both my Bachelor's and Master's Degrees from the Department of Computer Science, University of Pisa. During my Master Degree’s thesis, I started approaching the data stream processing research area. My main research interests are related to data stream processing applications in the networking domain, high performance network processing, data plane acceleration, SmartNICs and software defined networks. If you have any questions related to my work, please feel free to contact me.

Interests

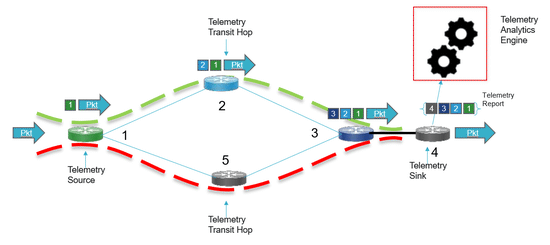

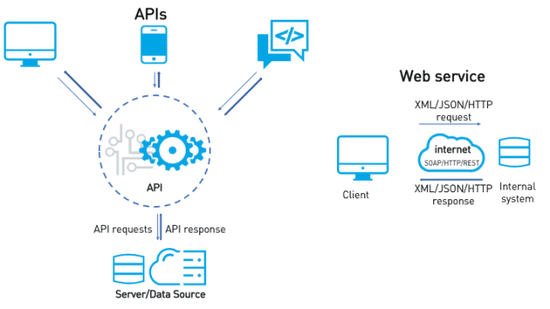

- Network monitoring

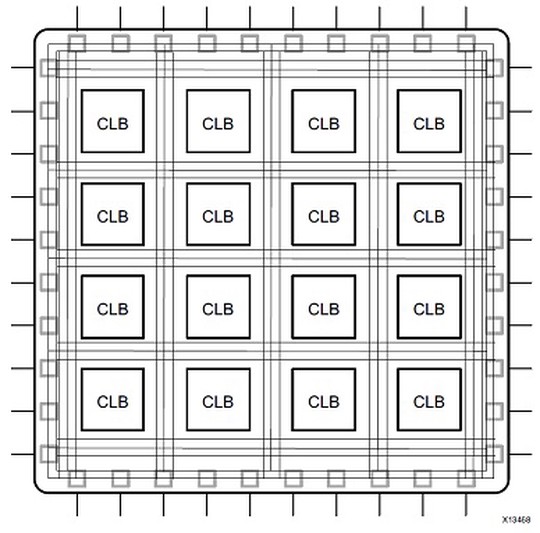

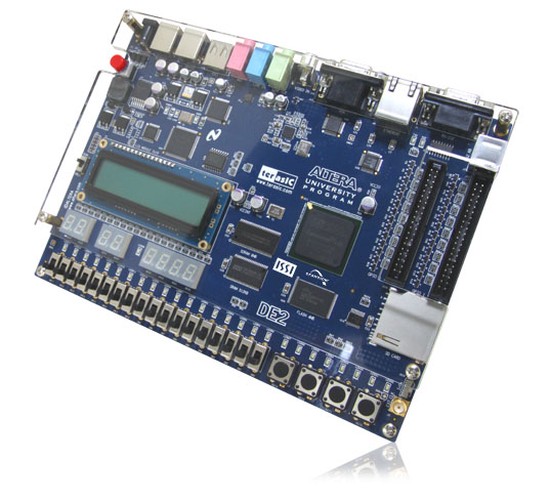

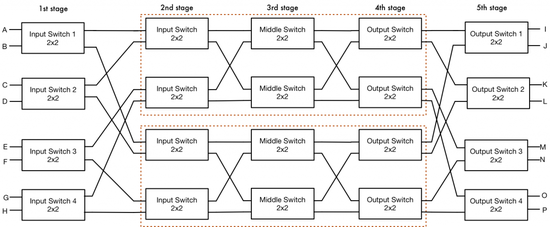

- High-perfomance network processing

- Data plane acceleration

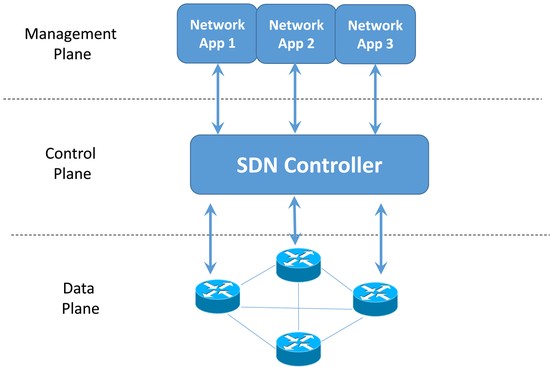

- Software Defined Networks

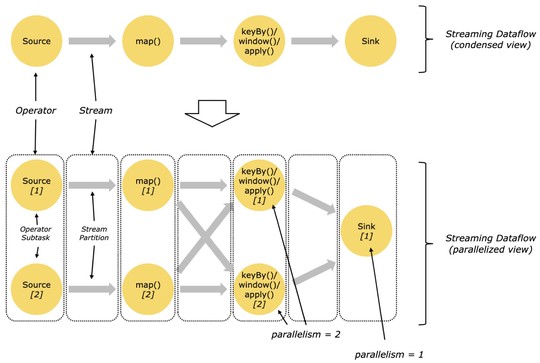

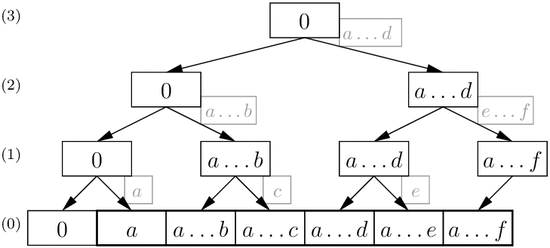

- Data Stream Processing

- Parallel computing

Education

-

Ph.D. in Information Engineering, currently enrolled

University of Pisa

-

M.Sc. in Computer Science and Networking, 2019

Scuola Superiore Sant'Anna and University of Pisa

-

B.Sc. in Computer Science, 2016

University of Pisa